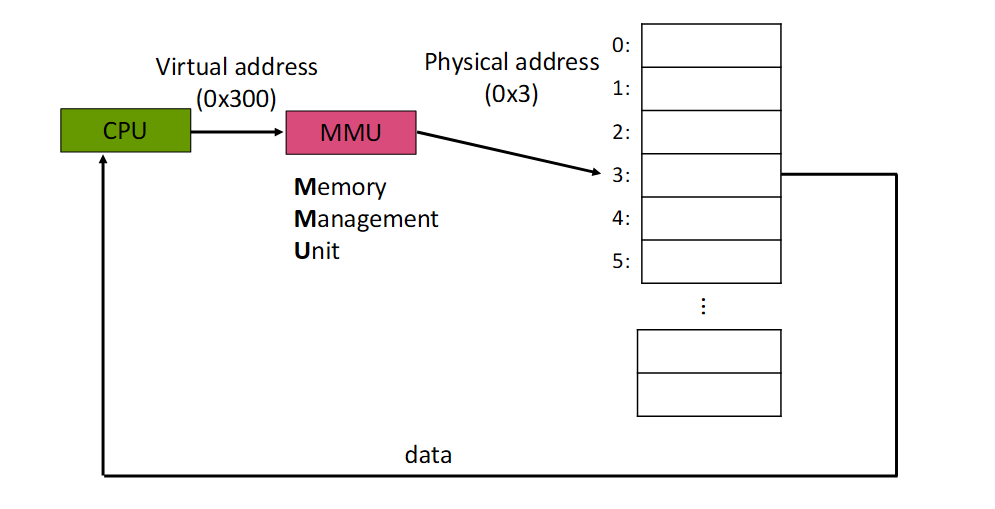

The MMU translates virtual addresses to physical addresses. This is necessary because in reality, all programs in our OS reference virtual addresses—this is a layer of abstraction given to each Process.

Once again we see that Operating systems are a protection system for processes.

The MMU is responsible for both page lookup (see address translation) and fetching pages from the disk (if it’s not currently loaded in RAM). This may also result in evicting another page to make more space (see page eviction).

Translation lookaside buffer (TLB)

(Me): so, we create this “virtual memory” to trick processes into thinking they have a contiguous address layout

(Medieval peasant): Would not thy abstraction swell the tally of mem’ry lookups?

(Me): well, yes. to deal with that we created the “translation lookaside buffer”

—@tomieinlove, original Tweet

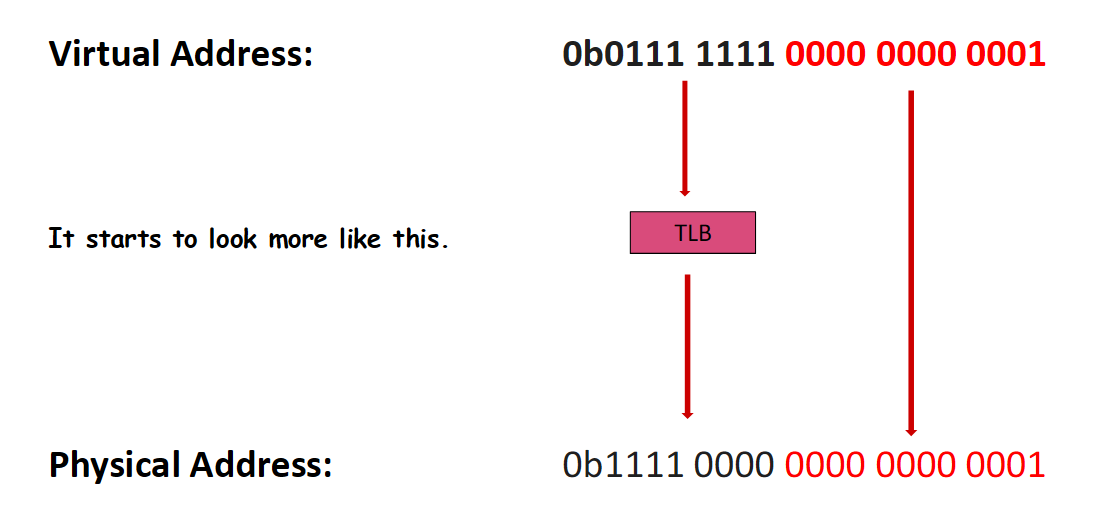

The MMU does not access the page table for every memory access. Instead, we add an additional dedicated cache to perform translation lookups.

This is a special piece of hardware memory that maps recent virtual page numbers to physical page frame translations. It’s a rather small cache so the MMU can quickly check all entries to see if a mapping exists.

- Entries contain the virtual page to physical frame mapping, dirty and permission bits, and a PID tag to enforce process isolation.

- Exploits temporal locality

- Usually made up of multiple levels (just like CPU L1, L2, L3 caches)

- Nowadays we have two L1 TLBs (64 or 128 entries), one for data, one for instructions.

- A bigger (~512 entries) L2 TLB that contains addresses for both instructions and data.

This is where the MMU looks first. If the MMU doesn’t find anything in the TLB, then we index into the page table and perform the translation.

Requires syncing with page table

- If a TLB entry is updated, the corresponding entry in the Page table must also be updated with any new dirty bit values.

- If a page is evicted from the page table then it must also be removed from the TLB, because otherwise future accesses will resolve to invalid memory locations

Maintaining process isolation

The TLB is a global cache shared across all processes. If we context switch to another process, all entries in the TLB become invalid and must be cleared.

- This is because virtual address translations are unique to each process and we can’t let another process access data that doesn’t belong to it.

- We perform a TLB flush to evict invalid addresses to make more room